## FireStar Plus

# **64-Bit CPU Single Chip Notebook Solution**

# **Addendum to Preliminary Data Book**

(FireStar Preliminary Data Book PN 912-2000-015 Rev. 1.0)

**OPTi Confidential**

**Preliminary**

Revision: 1.0 912-4000-013 October 3, 1997

#### Copyright

Copyright © 1997, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 888 Tasman Drive, Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

Note: Before designing contact OPTi for latest Product Alerts, Applications Notes, and Errata for this product line.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

**OPTi Inc.**

888 Tasman Drive Milpitas, CA 95035 Tel: (408) 486-8000 Fax: (408) 486-8001 www.opti.com

# **Table of Contents**

| 1.0 | Overview 1 |         |                                     |    |  |  |  |  |

|-----|------------|---------|-------------------------------------|----|--|--|--|--|

|     | 1.1        | Featur  | res                                 | 1  |  |  |  |  |

|     |            | 1.1.1   | Ultra DMA IDE Interface             | 1  |  |  |  |  |

|     |            | 1.1.2   | Synchronous DRAM on All Banks       | 1  |  |  |  |  |

|     |            | 1.1.3   | 2.5V CPU Interface                  | 1  |  |  |  |  |

|     |            | 1.1.4   | Redefinition of DRQ/DACK# Interface | 1  |  |  |  |  |

|     |            | 1.1.5   | Warnings                            | 2  |  |  |  |  |

|     | 1.2        | PCICL   | .K0-5 Usable as PIO0-5              | 3  |  |  |  |  |

|     | 1.3        | Suppo   | ort for 64Mb SDRAM                  | 3  |  |  |  |  |

|     | 1.4        | Dynan   | nic Clock Control Feature           | 3  |  |  |  |  |

|     | 1.5        | ATA33   | 3 Support Signal                    |    |  |  |  |  |

|     | 1.6        |         | mentation Changes                   |    |  |  |  |  |

|     | 1.7        |         | ved ACPI Functionality              |    |  |  |  |  |

|     | 1.8        | •       | ration of SMI# by SERR#             |    |  |  |  |  |

|     | 1.9        |         | al Upgrade Issues                   |    |  |  |  |  |

| 2.0 | Sia        | nal Def | finitions                           | e  |  |  |  |  |

| 2.0 | Oigi       | iai Dei |                                     |    |  |  |  |  |

| 3.0 | Clo        | ck Sigr | nal Specifications                  | 10 |  |  |  |  |

|     | 3.1        | CPU Ir  | nput Clock Recommendations          | 10 |  |  |  |  |

|     | 3.2        | PCI In  | put Clock Recommendations           | 10 |  |  |  |  |

| 4.0 | ВЮ         | S Reco  | ommendations                        | 10 |  |  |  |  |

|     | 4.1        | Basic   | Configuration                       | 10 |  |  |  |  |

|     | 4.2        | Prelim  | ninary Memory Configuration         | 11 |  |  |  |  |

|     | 4.3        | Setup   | Options                             | 11 |  |  |  |  |

|     |            | 4.3.1   | Refresh Mode                        | 11 |  |  |  |  |

|     |            | 4.3.2   | PCICLK                              | 11 |  |  |  |  |

|     |            | 4.3.3   | PCI Post Write                      | 11 |  |  |  |  |

|     |            | 4.3.4   | ISA Retry                           | 12 |  |  |  |  |

# Preliminary FireStar Plus

## **Table of Contents (cont.)**

|     |     | 4.3.5   | Buffered DMA                             | 12 |

|-----|-----|---------|------------------------------------------|----|

|     |     | 4.3.6   | L2 Cache Control                         | 12 |

|     |     | 4.3.7   | Cache 3-1-1-1-1-1 control                | 12 |

|     |     | 4.3.8   | CAS Precharge                            | 12 |

|     |     | 4.3.9   | DRAM Pipelining                          | 12 |

|     |     | 4.3.10  | DRAM Post Write                          | 13 |

|     |     | 4.3.11  | *CPU Write to DRAM Buffer                | 13 |

|     |     | 4.3.12  | SDRAM CAS#/Burst Order                   | 13 |

|     |     | 4.3.13  | *DRAM Byte Merge                         | 13 |

|     |     | 4.3.14  | *DRAM Read-Around                        | 13 |

|     |     | 4.3.15  | PCI Master Wait States                   | 13 |

|     |     | 4.3.16  | *PCI Write to DRAM Buffer                | 13 |

|     |     | 4.3.17  | *EDO Timing:                             | 14 |

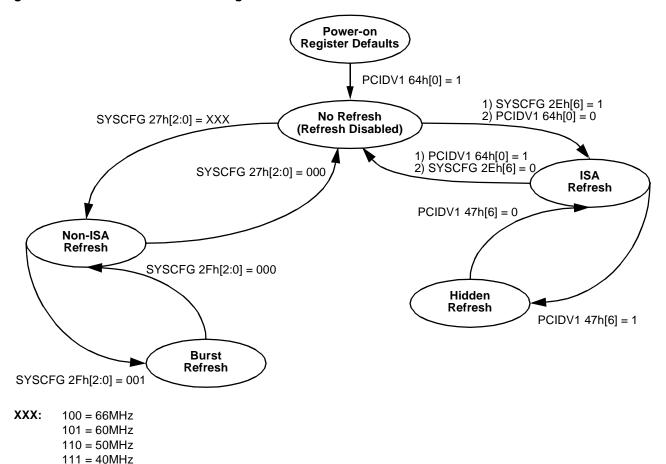

|     | 4.4 | Refres  | sh Modes                                 | 14 |

|     | 4.5 | FPM/E   | DO/SDRAM Detection Algorithm             | 14 |

|     | 4.6 | DRAM    | Sizing Algorithm                         | 17 |

|     |     | 4.6.1   | DRAM Detection and Sizing Algorithm      | 17 |

|     | 4.7 | SDRA    | M Sizing Algorithm                       | 20 |

|     | 4.8 | Integra | ated Local Bus Enhanced IDE Interface    | 21 |

|     |     | 4.8.1   | Bus Mastering IDE Controller             | 2′ |

|     |     | 4.8.2   | Programming the IDE Controller           | 24 |

|     |     | 4.8.3   | Programming Timing Information           | 27 |

|     |     | 4.8.4   | Bus Mastering Support Overview           | 34 |

|     |     | 4.8.5   | Physical Region Descriptor Table         | 35 |

|     |     | 4.8.6   | UltraDMA Mode Implementation             | 40 |

|     |     | 4.8.7   | Emulated Bus Mastering Mode              | 45 |

| 5.0 | PIR | Table f | for FireStar Plus                        | 47 |

|     | 5.1 | Overvi  | iew                                      | 47 |

|     | 5.2 | OPTi P  | PCI Interrupt Source Overview            | 47 |

|     | 5.3 | OPTi-S  | Suggested Link Value Scheme              | 47 |

|     |     | 5.3.1   | Proposed Usage                           | 47 |

|     |     | 5.3.2   | IRQ Selection Source and Register Offset | 48 |

|     |     |         |                                          |    |

## **Table of Contents (cont.)**

|     |             | 5.3.3          | Example of a PCI IRQ routing table:          | 49 |

|-----|-------------|----------------|----------------------------------------------|----|

| 6.0 | Inte        | rfacing        | g the FireStar Plus Chipset with the 82C602A | 51 |

|     | 6.1         | Purpo          | se of Using the 82C602A                      | 51 |

|     | 6.2         | Conne          | ectivity                                     | 51 |

|     |             | 6.2.1          | Strapping the 82C602A                        | 5′ |

|     |             | 6.2.2          | Using the 82C602A Internal RTC               | 51 |

|     |             | 6.2.3          | DREQ# and DACK# Connectivity                 | 5′ |

|     |             | 6.2.4          | Miscellaneous Power management connectivity  | 52 |

| Арр | endi        | к <b>А</b> . 6 | 602A Notebook Companion Chip                 | 55 |

|     | <b>A.</b> 1 | Overvi         | iew                                          | 55 |

|     |             | A.1.1          | Mode/Chipset Support                         | 55 |

|     |             | A.1.2          | RTC/CMOS RAM Register Access                 | 55 |

|     |             | A.1.3          | Design Notes                                 | 55 |

|     |             | A.1.4          | Reducing Suspend Power Consumption           | 55 |

|     |             | A.1.5          | Power Consumption Measurements               | 56 |

|     |             | A.1.6          | Internal Real-Time Clock (RTC)               | 56 |

|     | A.2         | Signal         | l Definitions                                | 65 |

|     | A.3         | Noteb          | ook Mode A Signal Descriptions               | 68 |

|     |             | A.3.1          | Clock and Reset Interface Signals            | 68 |

|     |             | A.3.2          | Interrupt Control Interface Signals          | 68 |

|     |             | A.3.3          | ISA DMA Arbiter Interface Signals            | 68 |

|     |             | A.3.4          | Data Bus and Control Interface Signals       | 69 |

|     |             | A.3.5          | Power Management Interface Signals           | 69 |

|     |             | A.3.6          | Real-Time Clock Interface Signals            | 70 |

|     |             | A.3.7          | IDE Interface Signals                        | 70 |

|     |             | A.3.8          | Power and Ground Pins                        | 7′ |

|     | A.4         | Schem          | natics                                       | 72 |

|     | A.5         | 82C60          | 2A Mechanical Package Outline                | 73 |

| Арр | endi        | kB. R          | Register Descriptions                        | 75 |

|     | B.1         | PCIDV          | /0 Register Space                            | 7  |

# OPTi Confidential

# Preliminary FireStar Plus

## **Table of Contents (cont.)**

| B.2      | SYSCF   | G Register Space                                           | 80  |

|----------|---------|------------------------------------------------------------|-----|

|          | B.2.1   | System Configuration Register Index/Data Programmable      | 80  |

| B.3      | PCIDV1  | Register Space                                             | 119 |

| Appendix | C. AC   | C Characteristics                                          | 145 |

| C.1      | CPU Int | erface Module AC Characteristics (66MHz - Preliminary)     | 145 |

| C.2      | DRAM (  | Controller Module AC Characteristics (66MHz - Preliminary) | 146 |

| C.3      | PCI Cor | ntroller Module AC Characteristics (66MHz - Preliminary)   | 147 |

| C.4      | ISA Cor | ntroller Module AC Characteristics (66MHz - Preliminary)   | 148 |

# **List of Figures**

| Figure 1-1  | Timing Diagram                                       | 2  |

|-------------|------------------------------------------------------|----|

| Figure 4-1  | Refresh Mode State Diagram                           | 15 |

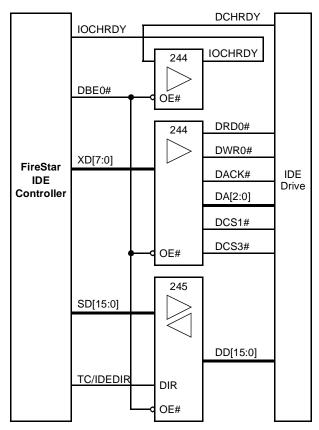

| Figure 4-2  | IDE Interface Using Individual TTL                   | 23 |

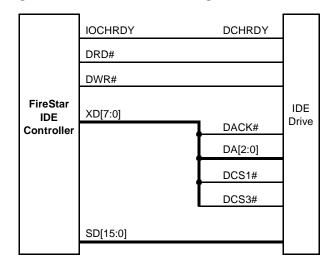

| Figure 4-3  | IDE Interface Using Zero-TTL                         | 23 |

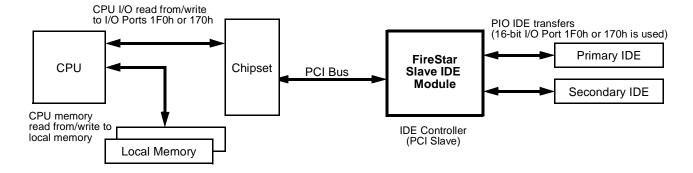

| Figure 4-4  | PIO Mode Configuration                               | 27 |

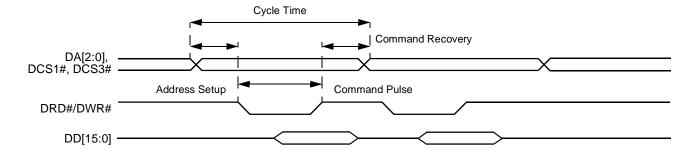

| Figure 4-5  | PIO Mode Cycle Timing                                | 28 |

| Figure 4-6  | IDE Interface Primary Channel Programming Flow Chart | 31 |

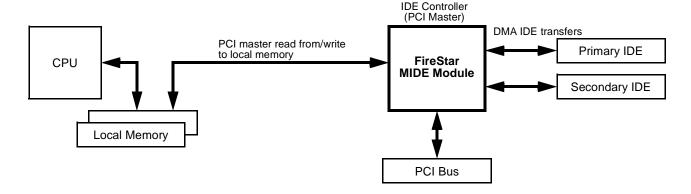

| Figure 4-7  | Master IDE Configuration                             | 34 |

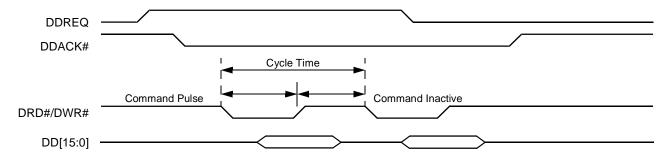

| Figure 4-8  | Multi-Word DMA Transfer Mode                         | 35 |

| Figure 4-9  | Single-Word DMA Transfer Mode                        | 35 |

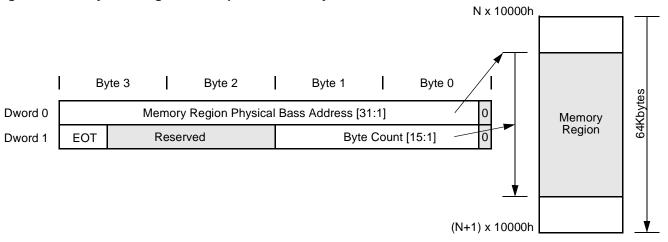

| Figure 4-10 | Physical Region Descriptor Table Entry               | 36 |

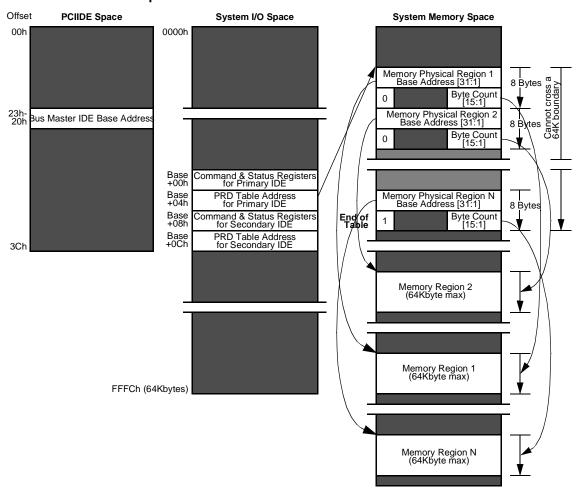

| Figure 4-11 | Bus Master IDE Operation                             | 39 |

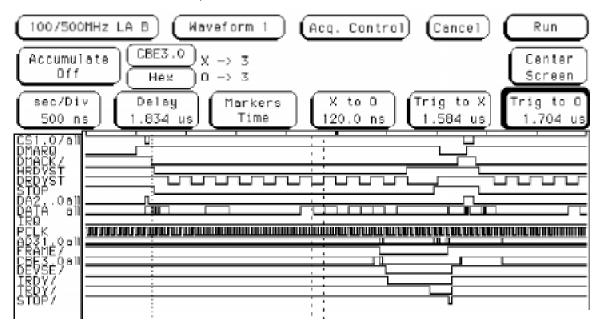

| Figure 4-12 | Ultra DMA Mode 0 Read, Command width = 120 ns        | 42 |

| Figure 4-13 | Ultra DMA mode 0 write                               | 43 |

| Figure 4-14 | Ultra DMA Mode 1 Read, Command width = 80ns          | 43 |

| Figure 4-15 | Ultra DMA mode 1 write                               | 44 |

| Figure 4-16 | Ultra DMA mode 2 read, Command width = 60ns          | 44 |

| Figure 4-17 | Ultra DMA mode 2 write                               | 45 |

| Figure 5-1  | PCI Interrupts Mapping Matrix                        | 50 |

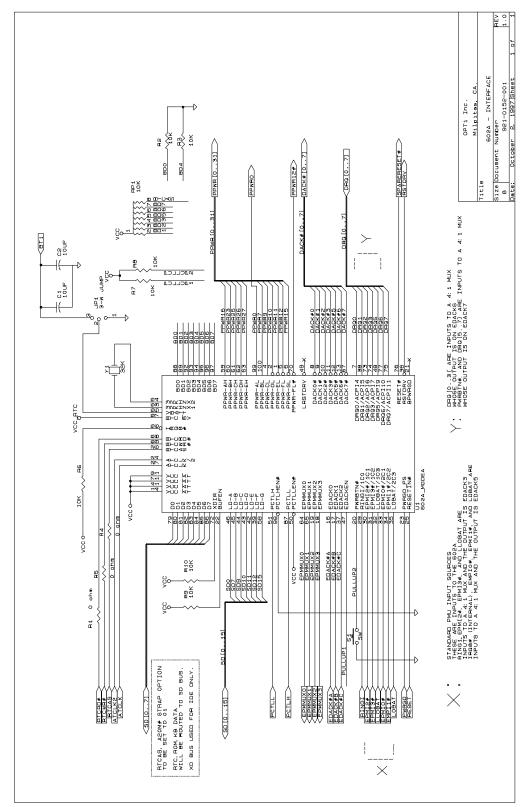

| Figure 6-1  | Schematics with 602A                                 | 53 |

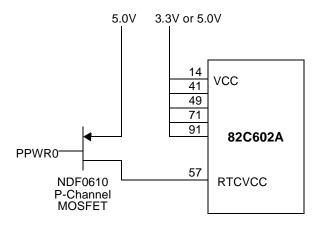

| Figure A-1  | RTCVCC Switching Circuit Example                     | 56 |

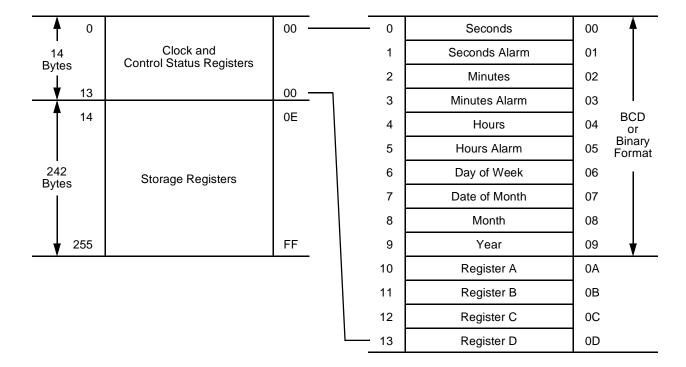

| Figure A-2  | RTC Address Map                                      | 57 |

| Figure A-3  | Update-Ended/Periodic Interrupt Relationship         | 59 |

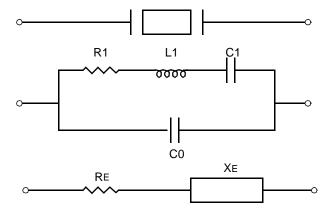

| Figure A-4  | Quartz Crystal Equivalent Circuit                    | 60 |

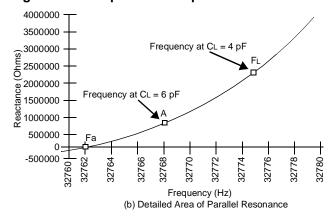

| Figure A-5  | Impedance Graph                                      | 60 |

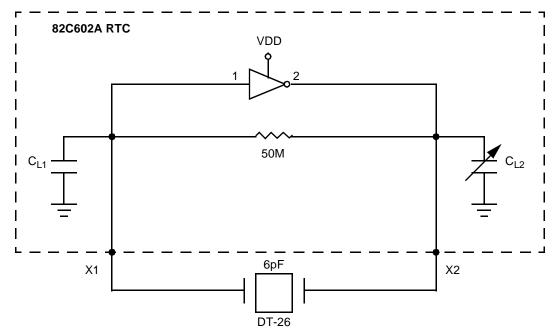

| Figure A-6  | RTC Oscillator Circuit Block Diagram                 | 61 |

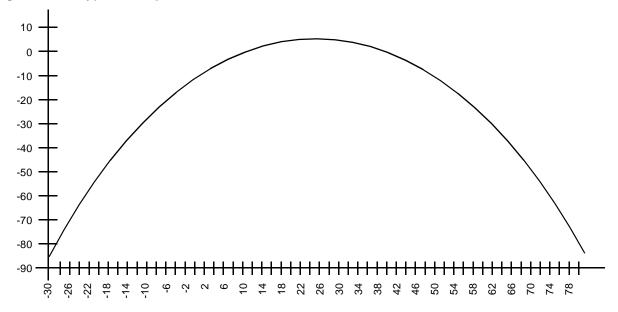

| Figure A-7  | Typical Temperature Characteristics                  | 61 |

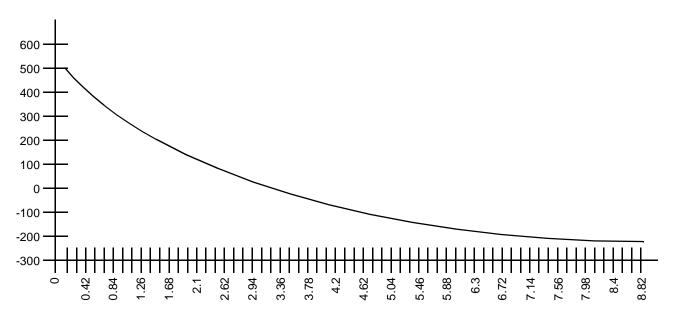

| Figure A-8  | Frequency Variation Versus Load Capacitance          | 62 |

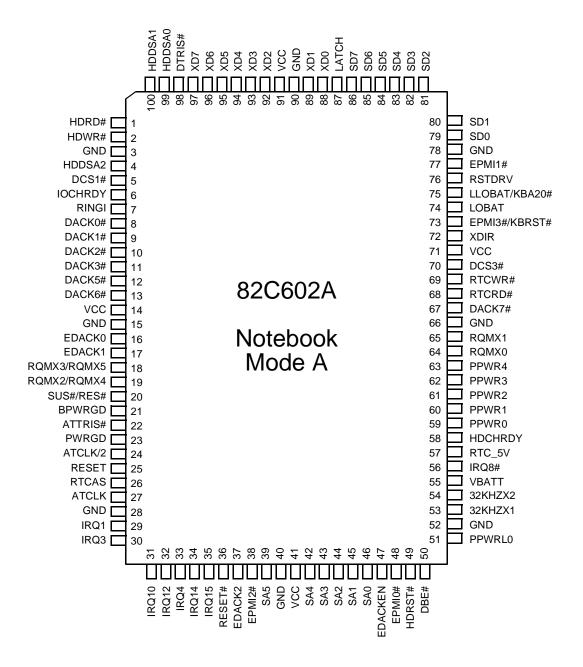

| Figure A-9  | Notebook Mode A Pin Diagram (100-Pin PQFP)           | 65 |

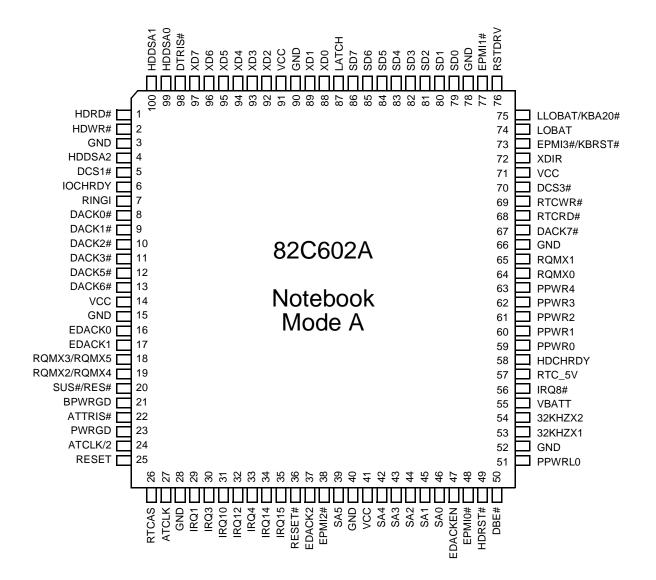

| Figure A-10 | Notebook Mode A Pin Diagram (100-Pin TQFP)           | 66 |

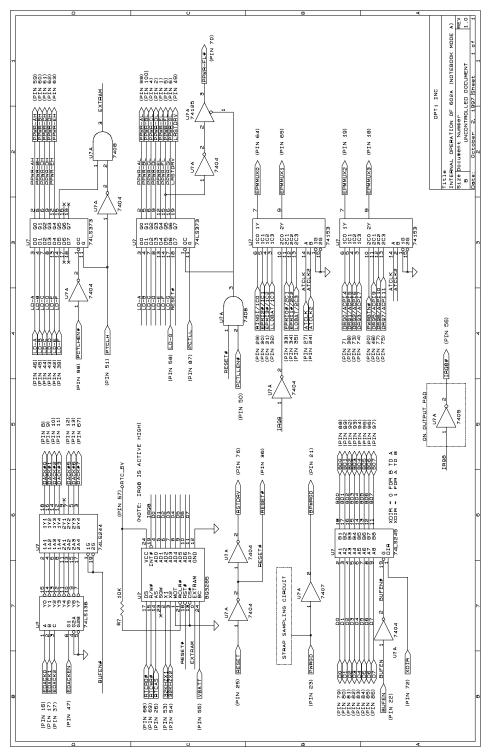

| Figure A-11 | 602A Mode A for FireStar Plus                        | 72 |

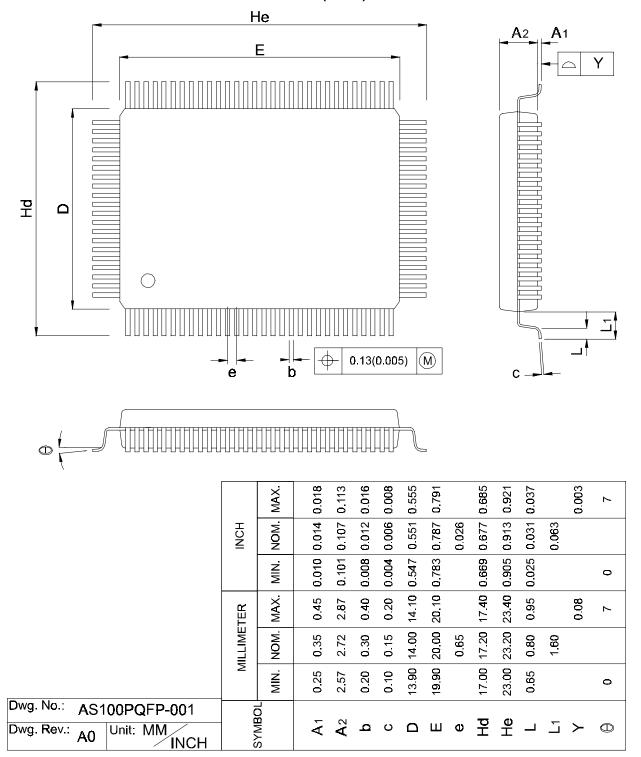

| Figure A-12 | 82C602A 100-Pin Plastic Quad Flat Pack (PQFP)        | 73 |

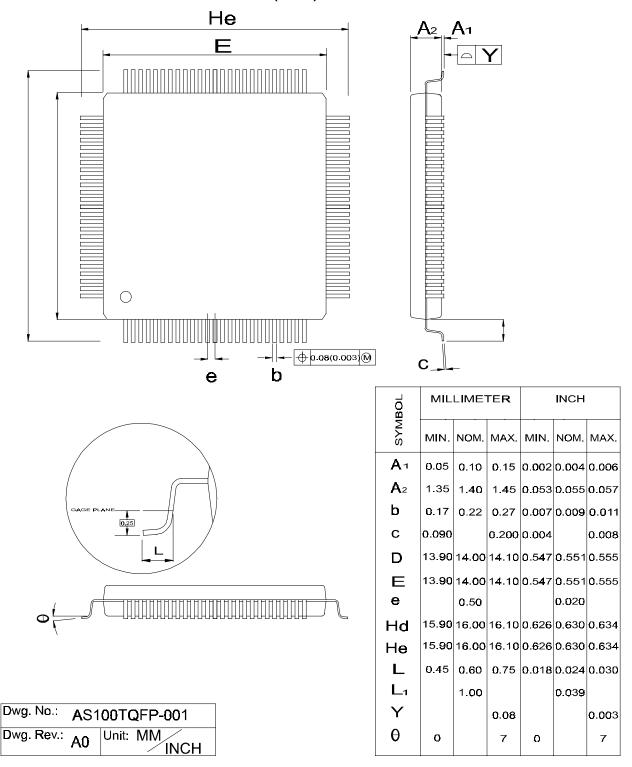

| Figure A-13 | 82C602A 100-Pin Thin Quad Pack (TQFP)                | 74 |

List of Figures (cont.)

# **List of Tables**

| Table 1-1  | DACK# Encoding                                           | 1   |

|------------|----------------------------------------------------------|-----|

| Table 1-2  | New DACK# Utilization                                    | 1   |

| Table 2-1  | Pin Changes from FireStar ACPI to FireStar Plus          | 6   |

| Table 2-2  | Alphabetical Pin Cross-Reference List                    | 7   |

| Table 4-1  | Programming Size Registers                               | 19  |

| Table 4-2  | IDE Pin Programming Registers                            | 21  |

| Table 4-3  | General IDE Control Line Assignment                      | 23  |

| Table 4-4  | Enabling/Disabling Access to IDE I/O Space Registers     | 24  |

| Table 4-5  | IDE Interface Control Registers                          | 25  |

| Table 4-6  | IDE Timing Control "Common Timing"                       | 28  |

| Table 4-7  | IDE Timing Control "Independent Timing"                  | 29  |

| Table 4-8  | Independent Timing Selection Options for Primary Channel | 32  |

| Table 4-9  | 16-Bit Timing Parameters with 33MHz PCI Bus              | 32  |

| Table 4-10 | 16-Bit Timing Parameters with 25MHz PCI Bus              | 33  |

| Table 4-11 | Physical Region Descriptor Table Entry                   | 35  |

| Table 4-12 | Bus Master IDE Registers                                 | 36  |

| Table 4-13 | DMA Mode Programming Bits                                | 37  |

| Table 4-14 | IDE Interrupt Routing Chart                              | 39  |

| Table 4-15 | IDE Interrupt Selection Registers                        | 40  |

| Table 4-16 | Emulated Bus Master Control Registers                    | 46  |

| Table 6-1  | DACK# Encoding                                           | 51  |

| Table 6-2  | New DACK# Utilization                                    | 51  |

| Table A-1  | Mode Strapping Options                                   | 55  |

| Table A-2  | Typical Current Consumption Figures for RTC Power        | 56  |

| Table A-3  | Typical Current Consumption Figures for Digital Power    | 56  |

| Table A-4  | Time, Alarm, and Calendar Formats                        | 57  |

| Table A-5  | Square-Wave Frequency/Periodic Interrupt Rate            | 58  |

| Table A-6  | Crystal Parameters                                       | 59  |

| Table A-7  | Control/Status Registers Summary                         | 63  |

| Table A-8  | Register A                                               | 63  |

| Table A-9  | Register B                                               | 63  |

| Table A-10 | Register C                                               | 64  |

| Table A-11 | Register D                                               | 64  |

| Table A-12 | Notebook Mode A - Numerical Pin Cross-Reference List     | 67  |

| Table A-13 | Notebook Mode A - Alphabetical Pin Cross-Reference List  | 67  |

| Table B-1  | PCIDV0 00h-FFh                                           | 75  |

| Table B-2  | SYSCFG Base Select Register                              | 80  |

| Table B-3  | SYSCFG 00h-2Fh                                           | 80  |

| Table B-4  | SYSCFG 30h-FFh (Power Management)                        | 96  |

| Table B-5  | PCIDV1 00h-FFh                                           | 119 |

List of Tables (cont.)

## **64-Bit CPU Single Chip Notebook Solution**

#### 1.0 Overview

This section describes the follow-on chip to the OPTi FireStar ACPI solution, the FireStar Plus. The key features of this new product can be summarized as follows.

- Mostly backward-compatible in pin function and register set with FireStar ACPI (some PIO functions have been moved from critical pins to improve timing)

- Implements ATA-33 (Ultra DMA) IDE Interface, with support for all modes

- Supports 2.5V CPUs

- · Incorporates MA13 support for 64Mb SDRAM chips

- Incorporates 64Mb EDO DRAM support

- Enables use of synchronous DRAM on all six banks (original FireStar chip limited synchronous DRAM to the first four banks)

- Allows redefinition of many interface pins for better utilization of chipset PIO features (many new function pins are easily available).

#### 1.1 Features

The following paragraphs describe the feature set changes between FireStar ACPI and FireStar Plus.

#### 1.1.1 Ultra DMA IDE Interface

The ATA33 specification for synchronous bus mastering IDE, also known as Ultra DMA, is fully supported by FireStar Plus.

#### 1.1.2 Synchronous DRAM on All Banks

The original FireStar chip supports synchronous DRAM only on RAS0-3#. FireStar Plus also supports synchronous DRAM on RAS4-5#. The additional functionality is selected through register bits that are already defined on the FireStar ACPI part.

#### 1.1.3 2.5V CPU Interface

FireStar Plus supports newer CPUs with I/O voltage requirements as low as 2.5V. The pin redefinition is as follows.

- Pins E8, G5, T5, and W5 are now VCC\_CPU and can be powered at 2.5V or 3.3V.

- Pins K5, H22, and AB19 are now VCC\_CORE and must always be powered at 3.3V.

- Pin M5, CPUCLKIN, must receive a clock on the VCC\_CPU plane. So if a 2.5V CPU is used, this clock should also be 2.5V.

The 2.5V interface is a strap-selected option. It is selected by a strap on pin B7 (new MA13 pin). If B7 is sensed low at reset, the CPU interface is 3.3V; if sensed high along with TMS (pin AB5) low, the CPU interface is 2.5V.

#### 1.1.4 Redefinition of DRQ/DACK# Interface

The 7 pins assigned to DACK0-7# can be redefined to improve availability of PIO pins.

Table 1-1 DACK# Encoding

| Original Name | New Signal | Decoder Input | Decoder Output                               |

|---------------|------------|---------------|----------------------------------------------|

| DACK0# (O)    | EDACK0 (O) | А             | DACK0-7# correspond to decoder outputs Y0-Y7 |

| DACK1# (O)    | EDACK1 (O) | В             |                                              |

| DACK2# (O)    | EDACK2 (O) | С             |                                              |

#### Table 1-2 New DACK# Utilization

| Original Name | New Signal | Mux Input | ATCLK /2 (B) | ATCLK (A) | Muxed Signals | Control PCIDV1 |

|---------------|------------|-----------|--------------|-----------|---------------|----------------|

| DACK3# (O)    | EPMMUX0    | C0        | 0            | 0         | RINGI         |                |

|               | (I) or     | C1        | 0            | 1         | EPMI2#        |                |

|               | EDACKEN    | C2        | 1            | 0         | EPMI3#        |                |

|               | (O)        | C3        | 1            | 1         | LLOBAT        |                |

912-4000-013 Revision: 1.0

| Original Name | New Signal | Mux Input | ATCLK /2 (B) | ATCLK (A) | Muxed Signals  | Control PCIDV1 |

|---------------|------------|-----------|--------------|-----------|----------------|----------------|

| DACK5# (O)    | EPMMUX1    | C0        | 0            | 0         | IRQ8# or ACPI8 | BDh[4]         |

|               | (1)        | C1        | 0            | 1         | EPMI0#         |                |

|               |            | C2        | 1            | 0         | EPMI1#         |                |

|               |            | C3        | 1            | 1         | LOBAT          |                |

| DACK6# (O)    | EPMMUX2    | C0        | 0            | 0         | DRQ0 or ACPI4  | BDh[0]         |

|               | (1)        | C1        | 0            | 1         | DRQ1 or ACPI5  | BDh[1]         |

|               |            | C2        | 1            | 0         | DRQ2 or ACPI6  | BDh[2]         |

|               |            | C3        | 1            | 1         | DRQ3 or ACPI7  | BDh[3]         |

| DACK7# (O)    | EPMMUX3    | C0        | 0            | 0         | PWRBTN#        |                |

|               | (1)        | C1        | 0            | 1         | DRQ5 or ACPI9  | BDh[5]         |

|               |            | C2        | 1            | 0         | DRQ6 or ACPI10 | BDh[6]         |

|               |            | C3        | 1            | 1         | DRQ7 or ACPI11 | BDh[7]         |

While the new definition only involves circuit modifications to the DACK0-7# pins, the overall gain is much greater when used with the 82C602A Companion Chip in its Viper Notebook Mode A configuration.

- 8 power management inputs are now available, muxed in with the DRQs and IRQ8# on the four EPMMUX pins.

- 7 full-featured PIO pins are available on the former FireStar DRQ0-7 pins and IRQ8# pin. The number of pins is actually 8, but is reduced by 1 because one must be programmed as ATCLK/2.

- 12 PPWR outputs are generated by latching the SD bus lines from PCTLH (FireStar PPWRL) and PCTLL (FireStar RSTDRV).

- The ISA bus RSTDRV signal is now generated by the 82C602A chip, so that the FireStar RSTDRV pin can be used for PPWR generation (power control latch control signal). If the extra PPWR signals are not needed, the FireStar RSTDRV pin becomes useful as a full-featured PIO pin.

Note: RINGI, PWRBTN#, and IRQ8# are selected with ATCLK and ATCLK/2 both low. This arrangement allows the chipset to monitor these signals for their wakeup function from resume even if the system is in Suspend mode (with ATCLK and ATCLK/2 both fixed low).

These options are selectable through the registers shown below.

| PCIDV1 | Name                                        | 7                                         | 6                                         | 5                                                             | 4                                                          | 3                                                                                | 2                                                        | 1                                                                            | 0                                                                          |

|--------|---------------------------------------------|-------------------------------------------|-------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| BCh    | 82C602A<br>Extended<br>Mode Regis-<br>ter 1 | Reserved                                  | Reserved                                  | EDACK-<br>EN# Polarity<br>0=Active<br>low<br>1=Active<br>high | Share NOWS# input with DCS3# out- put 0=No (default) 1=Yes | Share IOCHCK# with SERR# 0=No (default) 1=Yes (input qualified by port 061h bit) | Pin AE18<br>Function<br>0=IRQSER<br>1=DDRQ1<br>(default) | Extended<br>Mode pin<br>J22 Usage<br>0=EPM-<br>MUX0 (I)<br>1=EDACK<br>EN (O) | DACK0-7#<br>Extended<br>Mode<br>(82C602A<br>mode)<br>0=Disable<br>1=Enable |

| BDh    | 82C602A<br>Extended<br>Mode Regis-<br>ter 2 | EPMMUX3<br>C3 Input<br>0=DRQ7<br>1=ACPI11 | EPMMUX3<br>C2 Input<br>0=DRQ6<br>1=ACPI10 | EPMMUX3<br>C1 Input<br>0=DRQ5<br>1=ACPI9                      | EPMMUX1<br>C0 Input<br>0=IRQ8#<br>1=ACPI8                  | EPMMUX2<br>C3 Input<br>0=DRQ3<br>1=ACPI7                                         | EPMMUX2<br>C2 Input<br>0=DRQ2<br>1=ACPI6                 | EPMMUX2<br>C1 Input<br>0=DRQ1<br>1=ACPI5                                     | EPMMUX2<br>C0 Input<br>0=DRQ0<br>1=ACPI4                                   |

#### 1.1.5 Warnings

1. Until the Extended Mode option has been programmed, DACK3-7# will be driving out against the

signal input muxes. It is therefore important to ensure that the logic will not be harmed by this arrangement

(the FireStar outputs safely accept being driven by external logic in this mode).

- EDACKEN is an option used to ensure proper ISA master operation. It prevents the EDACK decoder from glitching its DACK# outputs during EDACK switching. If ISA masters are not supported in the system, this option is not needed (tie the EDACK line high on the 82C602A).

- There are no provisions to block conflicts in case more than one pin is programmed to the same function. For example, if a PIO pin is programmed to be ACPI8-11, and the Extended Mode option also enables EPMMUX1 to bring in ACPI8-11, the results are unpredictable.

#### 1.2 PCICLK0-5 Usable as PIO0-5

The PIO0-5 pin functions have been removed from their original CPU and memory interface pins to enable better timing control on these lines. These PIO functions have been transferred to PCICLK0-5 so that all the output PIO functions are now available on these pins. The following restrictions must be observed in properly utilizing these pins.

- PCICLK0: This pin defaults to its PCICLK output function.

Therefore, the connected device must be able to accept a 33MHz clock until the BIOS reprograms the pin. Be sure to program this pin to an appropriate function/level before entering Suspend.

- PCICLK1-2/GNT1-2#: If strapped for their GNTx# function, these pins default to a high state. Suspend state is controlled through PCIDV1 72h[5:4].

- PCICLK3/CMD#/DIRTY: If strapped for the CMD#/DIRTY function, this pin defaults to a high state. Suspend state is controlled through PCIDV1 73h[7:6].

- PCICLK4/ATCLK: If strapped for the ATCLK function, this pin outputs an 8MHz signal which the connected device must be able to accept until the BIOS has had a chance to

reprogram the pin. Be sure to program this pin to an appropriate function/level before entering Suspend.

PCICLK5/BALE: If strapped for the BALE function, this pin defaults to a low state. Be sure to program this pin to an appropriate function/level before entering Suspend.

**Note:** The Suspend mode setting of the original PIO0-5 pins, through bit 7 of the respective PIO Function Register, remains with the original pins. Thus:

- PCIDV1 80h[7] controls CDOE# (P100)

- PCIDV1 81h[7] controls TAGWE# (P101)

- PCIDV1 82h[7] controls ADSC# (P102)

- PCIDV1 83h[7] controls ADV# (P103)

- PCIDV1 84h[7] controls RAS2# (P104)

- PCIDV1 85h[7] controls RAS1#. (P105)

#### 1.3 Support for 64Mb SDRAM

The MA13 address line is now provided on B7. Set SYSCFG ACh[5]=1 to enable the MA13 pin. Note that B7 is also available as the DCC pin, and is additionally used as the CPU voltage threshold strap option.

MA13 is switchable between 4 and 16mA along with the other MA lines. It is on the DRAM power plane.

#### 1.4 Dynamic Clock Control Feature

FireStar Plus allows the CPU clock frequency to be changed through a STPCLK# generation sequence. This feature, Dynamic Clock Control (DCC), is available as an alternative to the MA13 pin B7.

Because this pin is used as a strap option at reset time, the default state of the bit is always the same as the strap-selected option. Therefore, the system logic must be designed with this in mind.

| SYSCFG | Name                                    | 7        | 6        | 5                                                              | 4                                                                                | 3                                                      | 2                                                                             | 1           | 0                                                                                             |

|--------|-----------------------------------------|----------|----------|----------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------|

| ACh    | Dynamic<br>Clock<br>Control<br>Register | Reserved | Reserved | B7 Pin<br>Function<br>Select<br>0=DCCEN<br>(default)<br>1=MA13 | Block<br>other<br>STPCLK#<br>sources<br>when<br>DCCEN<br>active<br>0=No<br>1=Yes | Current<br>state of<br>DCCEN<br>pin<br>0=Low<br>1=High | STPCLK# D Delay from E change 00=0.5-0.7m 01=1.0-1.3m 10=1.7-2.0m 11=1.00-1.2 | OCCEN state | Activate/<br>de-acti-<br>vate fre-<br>quency<br>change<br>0=No<br>effect<br>1=Toggle<br>DCCEN |

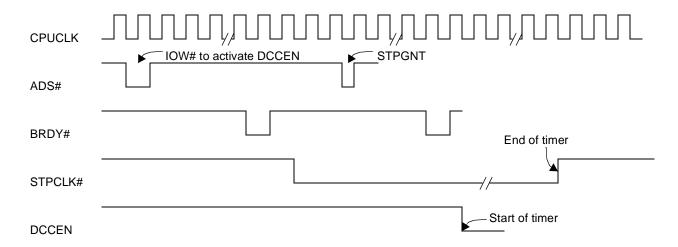

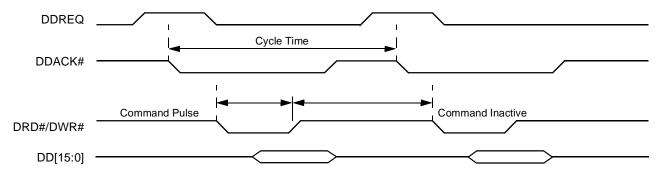

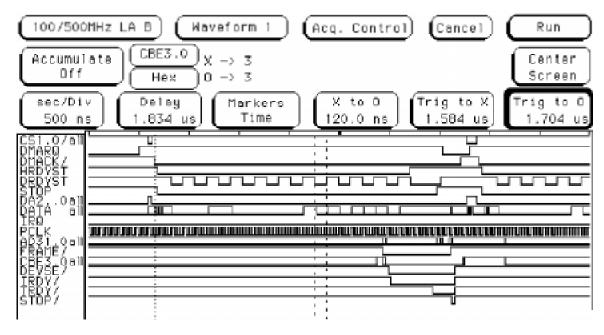

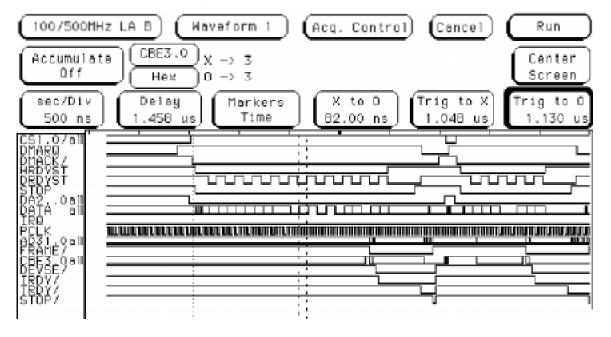

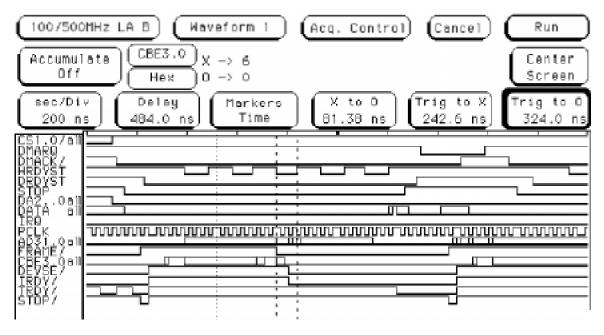

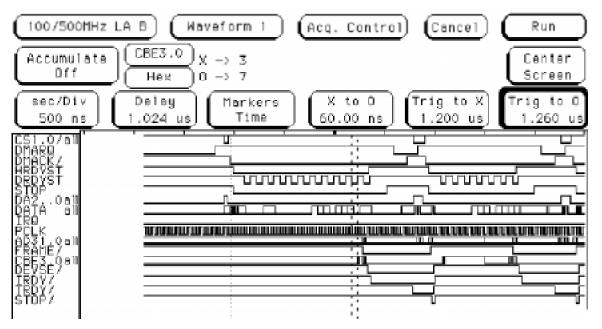

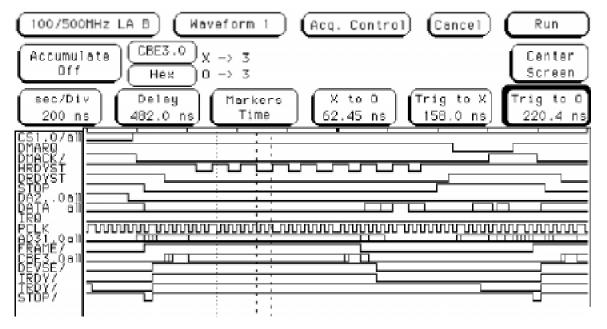

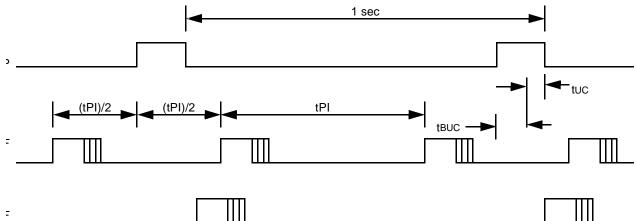

The timing for this feature is shown in Figure 1-1.

Figure 1-1 Timing Diagram

#### 1.5 ATA33 Support Signal

Current FireStar designs use the DRD# signals from the IDE controller to reverse the direction of the data buffer on read cycles. But FireStar Plus designs that take advantage of ATA33 will need an extra signal, IDEDIR, to control the direction of the buffer, since the read signal toggles during ATA33 transfers.

In FireStar Plus, the IDEDIR signal is superimposed on the ISA signal TC. This arrangement causes no conflict, since ISA cycles and IDE cycles are always exclusive of each other. The TC toggling does not have any effect on the IDE interface unless the DBE# signal for the specific drive buffer is active.

The IDEDIR signal is put on TC only during IDE cycles, so that the idle state of TC remains LOW at all other times. The register setting used to enable this functionality works as follows.

PCIDV1 52h[7] = 0; TC pin is TC PCIDV1 52h[7] = 1; TC pin is TC/IDEDIR

#### 1.6 Documentation Changes

The following bit was present in all previous FireStar production revisions but never documented.

PCIDV1 53h[0] = 0; All inputs (PCI requests) are not synchronized

PCIDV1 53h[0] = 1; Synchronize all inputs to PCICLK before passing to arbiter.

The default strapping for pin N24 and R23 described in the FireStar ACPI Data Book is incorrect. The correct default is RTCAS pulled up, A20M# pulled down.

### 1.7 Improved ACPI Functionality

**SCI Interrupt.** An SCI can now generate any interrupt from the group IRQ9,10,11,13. Selection bits for this function are shown below.

| PCIDV1 | Name                                     | 7        | 6        | 5        | 4        | 3        | 2                                                    | 1                                                                    | 0 |

|--------|------------------------------------------|----------|----------|----------|----------|----------|------------------------------------------------------|----------------------------------------------------------------------|---|

| EFh    | ACPI<br>Misc. Con-<br>trol Regis-<br>ter | Reserved | Reserved | Reserved | Reserved | Reserved | Select<br>IRQ13 as<br>level<br>mode<br>0=No<br>1=Yes | System IRQ<br>SCI<br>00=IRQ9 (de<br>01=IRQ10<br>10=IRQ11<br>11=IRQ13 |   |

**ACPI Input Polarity.** ACPI inputs now have individually selectable polarity. The "active" polarity is the one that causes an SCI. The new registers shown below select the

polarity of each ACPI input, regardless of the source (IRQ driveback, discrete PIO pin input, multiplexed PIO pin input, or multiplexed Extended Mode input).

| The defaults listed quarantee backward | compatibility with the fixed setting | s of the previous FireStar ACPI revision. |

|----------------------------------------|--------------------------------------|-------------------------------------------|

|                                        |                                      |                                           |

| PCIDV1 | Name                                            | 7                                                                     | 6                                                                     | 5                                                                         | 4                                                   | 3                                                                         | 2                                                                            | 1                                                                          | 0                                                                               |

|--------|-------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| DEh    | ACPI<br>Input<br>Polarity<br>Register<br>byte 0 | ACPI7<br>LID Event<br>active<br>when:<br>0=Low<br>1=High<br>(default) | ACPI6<br>EC# Event<br>active<br>when:<br>0=Low<br>(default)<br>1=High | ACPI5<br>USB#<br>Event<br>active<br>when:<br>0=Low<br>(default)<br>1=High | ACPI4 RI# Event active when: 0=Low (default) 1=High | ACPI3<br>FRI#<br>Event<br>active<br>when:<br>0=Low<br>(default)<br>1=High | ACPI2<br>STSCHG#<br>Event<br>active<br>when:<br>0=Low<br>(default)<br>1=High | ACPI1<br>DOCK#<br>Event<br>active<br>when:<br>0=Low<br>(default)<br>1=High | ACPI0<br>UNDOCK<br># Request<br>active<br>when:<br>0=Low<br>(default)<br>1=High |

| DFh    | ACPI<br>Input<br>Polarity<br>Register<br>byte 1 | Reserved                                                              | Reserved                                                              | Reserved                                                                  | Reserved                                            | ACPI11<br>Event<br>active<br>when:<br>0=Low<br>1=High<br>(default)        | ACPI10<br>Event<br>active<br>when:<br>0=Low<br>1=High<br>(default)           | ACPI9<br>Event<br>active<br>when:<br>0=Low<br>1=High<br>(default)          | ACPI8<br>Event<br>active<br>when:<br>0=Low<br>1=High<br>(default)               |

#### 1.8 Generation of SMI# by SERR#

FireStar Plus provides a practical means for SMM code to try to correct PCI errors signalled through SERR#. This feature allows SERR# going active to be handled as a Hot Docking Timeout event, PMI#34. In this way, it is possible to allow the system NMI handler to take care of the SERR# event in the normal way. If there is no NMI handler code present, SMM can step in and resolve the problem.

The feature is enabled as follows.

Set PCIDV1 68h[7:6]=11 to route SERR# to SMI instead of NMI. When this selection is used, the HDI PIO pin option must not be used.  Set SYSCFG EFh=08h to enable PMI#34. Note that the SYSCFG EFh timer functions of the HDI feature are not used in this application.

SERR# will now generate a PMI#34 event. The event is indicated in (and cleared by writing to) SYSCFG EAh[5].

This feature is particularly useful in conjunction with the 82C814 Docking Controller. If the 82C814 cannot complete a cycle to its secondary, it will retry its primary bus forever or until reset. But it can be programmed to generate SERR# after a certain number of retries. Converting SERR# to an SMI gives SMM code a chance to clear the 814 secondary and possibly fix the problem.

| PCIDV1 | Name                            | 7                                       | 6                                                  | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---------------------------------|-----------------------------------------|----------------------------------------------------|---|---|---|---|---|---|

| 68h    | PCICLK<br>Control<br>Register 1 | Source of<br>PMI#34<br>0=HDI<br>1=SERR# | SERR# generates: 0=NMI 1=SMI valid only if bit 7=1 |   |   |   |   |   |   |

#### 1.9 General Upgrade Issues

The following issues may affect FireStar Plus designs. Careful planning will minimize the design impact.

- The PIO0-5 pin functions have been moved from their original pin locations. Most designers could not access these PIO functions since they needed the default pin functionality. Designers should check their circuits for use of these PIO functions (now available on other pins).

- RAS5# is multiplexed with GWE#, which is on the CPU power plane. If a 2.5V CPU is used, the 2.5V RAS5# signal may not be appropriate for the DRAM that is used.

- The drive capability of the GWE# I/O cell is 4mA. If this pin is used as RAS5#, it is not possible to support more than 4 loads on this bank. Designers should only use x16 devices on this bank.

- The new SDCKE signal on A7 has been moved to the FS\_CORE power plane which is always 3.3V (SDRAMs can only be 3.3V devices). The drive capability on SDCKE has been increased to 16mA.

- CACS#/DIRTY when used as DIRTY is now 3.3V-tolerant instead of 5V-tolerant.

912-4000-013 Page 5

Revision: 1.0 October 3, 1997

## 2.0 Signal Definitions

Table 2-1 Pin Changes from FireStar ACPI to FireStar Plus

| Pin# | FireStar ACPI        | FireStar Plus                    | Comments                                           |

|------|----------------------|----------------------------------|----------------------------------------------------|

| P1   | CDOE#+PIO0           | CDOE#                            | PIO0 moved to Pin AB14                             |

| P3   | CACS#+DIRTY          | CACS#+DIRTY                      | On the FireStar Plus this pin is not 5V tolerant   |

| E9   | TAG0+CAS0#           | TAG0                             |                                                    |

| D9   | TAG1+CAS1#+START#    | TAG1                             |                                                    |

| C9   | TAG2+CAS2#+START#    | TAG2                             |                                                    |

| В9   | TAG3+CAS3#+SBOFF#    | TAG3                             |                                                    |

| A9   | TAG4+CAS4#+SDCKE     | TAG4                             |                                                    |

| D8   | TAG5+CAS5#+DWE#      | TAG5                             |                                                    |

| C8   | TAG6+CAS6#+SDCAS#    | TAG6                             |                                                    |

| B8   | TAG7+CAS7#+SDRAS#    | TAG7                             |                                                    |

| A10  | TAGWE#+PIO1          | TAGWE#                           | PIO1 moved to Pin AB17                             |

| P5   | ADSC#+PIO2           | ADSC#                            | PIO2 moved to Pin AB15                             |

| P2   | ADV#+PIO3            | ADV#                             | PIO3 moved to Pin AB20                             |

| E13  | RAS1#+SDCS1#+PIO5    | RAS1#+SDCS1#                     | PIO5 moved to Pin W22                              |

| B12  | RAS2#+SDCS2#+PIO4    | RAS2#+SDCS2#                     | PIO4 moved to Pin AA22                             |

| E22  | RAS4#+MA12           | RAS4#+SDCS4#+MA12                | This version of FireStar supports 6 banks of SDRAM |

| N1   | GWE#+RAS5#           | GWE#+RAS5#SDCS5#                 |                                                    |

| AB14 | PCICLK0              | PCICLK0+PIO0                     |                                                    |

| AB17 | GNT1#+PCICLK1        | GNT1#+PCICLK1+PIO1               |                                                    |

| AB15 | GNT2#+PCICLK2        | GNT2#+PCICLK2+PIO2               |                                                    |

| K22  | DACK0#/DACKA#+PPWR4  | DACK0#+PPWR4+EDACK0              |                                                    |

| K23  | DACK1#/DACKB#+PPWR5  | DACK1#+PPWR5+EDACK1              |                                                    |

| K24  | DACK2#/DACKC#+PPWR6  | DACK2#+PPWR6+EDACK2              |                                                    |

| K25  | DACK3#/DACKD#+PPWR7  | DACK3#+PPWR7+EDACKEN+<br>EPMMUX0 |                                                    |

| K26  | DACK5#/DACKE#+PPWR13 | DACK5#+PPWR13+EPMMUX1            |                                                    |

| J22  | DACK6#/DACKF#+PPWR14 | DACK6#+PPWR14+EPMMUX2            |                                                    |

| J23  | DACK7#/DACKG#+PPWR15 | DACK7#+PPWR15+EPMMUX3            |                                                    |

| AC25 | RSTDRV+PIO15         | RSTDRV+PIO15+PCTLL               |                                                    |

| AB20 | CMD#+DIRTY+PCICLK3   | CMD#+DIRTY+PCICLK3+PIO3          |                                                    |

| AA22 | ATCLK+PCICLK4        | ATCLK+PCICLK4+PIO4               |                                                    |

| W22  | BALE+PCICLK5         | BALE+PCICLK5+PIO5                |                                                    |

| M23  | TC+PPWR10            | TC+PPWR10+IDEDIR                 |                                                    |

| Pin#              | FireStar ACPI | FireStar Plus      | Comments |

|-------------------|---------------|--------------------|----------|

| AC23              | PPWRL+PPWR0#  | PPWRL+PPWR0#+PCTLH |          |

| В7                | Reserved      | MA13+DCCEN         |          |

| E8, G5,<br>T5, W5 | VCC_CORE      | VCC_CPU            |          |

Table 2-2 Alphabetical Pin Cross-Reference List

| Signal Name        | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|--------------------|------------|-------------|--------------|

| A20M#              | R3         | 0           | CPU          |

| AD0                | AD14       | I/O         | PCI          |

| AD1                | AC14       | I/O         | PCI          |

| AD2                | AF13       | 1/0         | PCI          |

| AD3                | AE13       | I/O         | PCI          |

| AD4                | AD13       | 1/0         | PCI          |

| AD5                | AC13       | I/O         | PCI          |

| AD6                | AF12       | 1/0         | PCI          |

| AD7                | AE12       | 1/0         | PCI          |

| AD8                | AD12       | 1/0         | PCI          |

| AD9                | AC12       | I/O         | PCI          |

| AD10               | AF11       | I/O         | PCI          |

| AD11               | AE11       | I/O         | PCI          |

| AD12               | AD11       | I/O         | PCI          |

| AD13               | AC11       | I/O         | PCI          |

| AD14               | AF10       | I/O         | PCI          |

| AD15               | AE10       | I/O         | PCI          |

| AD16               | AD10       | I/O         | PCI          |

| AD17               | AC10       | I/O         | PCI          |

| AD18               | AF9        | I/O         | PCI          |

| AD19               | AE9        | I/O         | PCI          |

| AD20               | AD9        | I/O         | PCI          |

| AD21               | AC9        | I/O         | PCI          |

| AD22               | AF8        | I/O         | PCI          |

| AD23               | AE8        | I/O         | PCI          |

| AD24               | AD8        | I/O         | PCI          |

| AD25               | AC8        | I/O         | PCI          |

| AD26               | AB8        | I/O         | PCI          |

| AD27               | AF7        | I/O         | PCI          |

| AD28               | AE7        | I/O         | PCI          |

| AD29               | AD7        | I/O         | PCI          |

| AD30               | AC7        | I/O         | PCI          |

| AD31               | AF6        | I/O         | PCI          |

| ADS#               | V5         | 1           | CPU          |

| ADSC#              | P5         | 0           | CPU          |

| ADV#               | P2         | 0           | CPU          |

| AEN+PPWR11         | M22        | I/O         | ISA          |

| AHOLD              | U3         | 0           | CPU          |

| ATCLK+PCICLK4+PIO4 | AA22       | 0           | ISA          |

| BALE+PCICLK5+PIO5  | W22        | 0           | ISA          |

| BE0#               | W1         | 1           | CPU          |

| BE1#               | W2         | ı           | CPU          |

| BE2#               | W3         |             | CPU          |

| BE3#               | W4         |             | CPU          |

| BE4#               | V1         | 1           | CPU          |

| BE5#               | V2         | ı           | CPU          |

| Signal Name                                 | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|---------------------------------------------|------------|-------------|--------------|

| BE6#                                        | V3         | -           | CPU          |

| BE7#                                        | V4         | ı           | CPU          |

| BOFF#                                       | R5         | I/O         | CPU          |

| BRDY#                                       | U5         | 0           | CPU          |

| BWE#                                        | P4         | 0           | CPU          |

| CACHE#                                      | T2         | ı           | CPU          |

| CACS#+DIRTY                                 | P3         | I/O         | CPU          |

| CAS0#+SDDQM0#                               | B10        | 0           | DRAM         |

| CAS1#+SDDQM1#                               | C10        | 0           | DRAM         |

| CAS2#+SDDQM2#                               | D10        | 0           | DRAM         |

| CAS3#+SDDQM3#                               | A11        | 0           | DRAM         |

| CAS4#+SDDQM4#                               | B11        | 0           | DRAM         |

| CAS5#+SDDQM5#                               | C11        | 0           | DRAM         |

| CAS6#+SDDQM6#                               | D11        | 0           | DRAM         |

| CAS7#+SDDQM7#                               | A12        | 0           | DRAM         |

| C/BE0#                                      | AD15       | I/O         | PCI          |

| C/BE1#                                      | AC15       | I/O         | PCI          |

| C/BE2#                                      | AF14       | I/O         | PCI          |

| C/BE3#                                      | AE14       | I/O         | PCI          |

| CDOE#                                       | P1         | 0           | CPU          |

| CLKRUN#+PIO6                                | AF16       | I/O         | PCI          |

| CMD#+DIRTY+PCICLK3+<br>PIO3                 | AB20       | I/O         | ISA          |

| CPAR                                        | AC17       | I/O         | PCI          |

| CPUCLKIN                                    | M5         | ı           | CPU          |

| CPUINIT                                     | AD6        | 0           | CPU          |

| CPURST                                      | R1         | 0           | CPU          |

| D/C#                                        | Т3         | I           | CPU          |

| DACK0#/DACKA#+<br>PPWR4+EDACK0              | K22        | 0           | ISA          |

| DACK1#/DACKB#+<br>PPWR5+EDACK1              | K23        | 0           | ISA          |

| DACK2#/DACKC#+<br>PPWR6+EDACK2              | K24        | 0           | ISA          |

| DACK3#/DACKD#+<br>PPWR7+EDACKEN+EPM<br>MUX0 | K25        | I/O         | ISA          |

| DACK5#/DACKE#+<br>PPWR13+EPMMUX1            | K26        | I/O         | ISA          |

| DACK6#/DACKF#+<br>PPWR14+EPMMUX2            | J22        | I/O         | ISA          |

| DACK7#/DACKG#+<br>PPWR15+EPMMUX3            | J23        | I/O         | ISA          |

| DBEW#+IDE1_DACK#+<br>DWR#                   | H24        | 0           | ISA          |

| DDRQ0+PIO9                                  | H25        | I/O         | ISA          |

| DEVSEL#                                     | AF15       | I/O         | PCI          |

| DRQ0/DRQA+PIO25                             | M24        | I/O         | ISA          |

| DRQ1/DRQB+PIO26                             | M25        | I/O         | ISA          |

| Signal Name        | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|--------------------|------------|-------------|--------------|

| DRQ2/DRQC+PIO27    | M26        | I/O         | ISA          |

| DRQ3/DRQD+PIO28    | L23        | I/O         | ISA          |

| DRQ5/DRQE+PIO29    | L24        | I/O         | ISA          |

| DRQ6/DRQF+PIO30    | L25        | I/O         | ISA          |

| DRQ7/DRQG+PIO31    | L26        | I/O         | ISA          |

| DWE#+SDWE#         | E10        | 0           | DRAM         |

| EADS#+WB/WT#       | T4         | 0           | CPU          |

| FERR#              | T1         | -           | CPU          |

| FRAME#             | AB9        | I/O         | PCI          |

| GND                | AA6        | G           |              |

| GND                | AA13       | G           |              |

| GND                | AA14       | G           |              |

| GND                | AA21       | G           |              |

| GND                | AB13       | G           |              |

| GND                | E14        | G           |              |

| GND                | F6         | G           |              |

| GND                | F13        | G           |              |

| GND                | F14        | G           |              |

| GND                | F21        | G           |              |

| GND                | N5         | G           |              |

| GND                | N6         | G           |              |

| GND                | N21        | G           |              |

| GND                | P6         | G           |              |

| GND                | P21        | G           |              |

| GND                | P22        | G           |              |

| GNT0#              | AD16       | 0           | PCI          |

| GNT1#+PCICLK1+PIO1 | AB17       | 0           | PCI          |

| GNT2#+PCICLK2+PIO2 | AB15       | 0           | PCI          |

| GNT3#              | AC18       | 0           | PCI          |

| GWE#+RAS5#+SDSC5#  | N1         | 0           | CPU          |

| HA3                | Y4         | I/O         | CPU          |

| HA4                | Y3         | I/O         | CPU          |

| HA5                | Y2         | I/O         | CPU          |

| HA6                | Y1         | I/O         | CPU          |

| HA7                | AA4        | I/O         | CPU          |

| HA8                | AA3        | I/O         | CPU          |

| HA9                | AA2        | I/O         | CPU          |

| HA10               | AA1        | I/O         | CPU          |

| HA11               | AB4        | I/O         | CPU          |

| HA12               | AB3        | I/O         | CPU          |

| HA13               | AB2        | I/O         | CPU          |

| HA14               | AB1        | I/O         | CPU          |

| HA15               | AC3        | I/O         | CPU          |

| HA16               | AC2        | I/O         | CPU          |

| HA17               | AC1        | I/O         | CPU          |

| HA18               | AD2        | I/O         | CPU          |

|                    |            |             |              |

912-4000-013 Revision: 1.0

# Preliminary FireStar Plus

|             | D:         | D:          | D            |

|-------------|------------|-------------|--------------|

| Signal Name | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

| HA19        | AD1        | I/O         | CPU          |

| HA20        | AE1        | I/O         | CPU          |

| HA21        | AF1        | I/O         | CPU          |

| HA22        | AE2        | I/O         | CPU          |

| HA23        | AF2        | I/O         | CPU          |

| HA24        | AD3        | I/O         | CPU          |

| HA25        | AE3        | I/O         | CPU          |

| HA26        | AF3        | I/O         | CPU          |

| HA27        | AC4        | I/O         | CPU          |

| HA28        | AD4        | I/O         | CPU          |

| HA29        | AE4        | I/O         | CPU          |

| HA30        | AF4        | I/O         | CPU          |

| HA31        | AC5        | I/O         | CPU          |

| HD0         | N2         | I/O         | CPU          |

| HD1         | N3         | I/O         | CPU          |

| HD2         | N4         | I/O         | CPU          |

| HD3         | M1         | I/O         | CPU          |

| HD4         | M2         | I/O         | CPU          |

| HD5         | M3         | I/O         | CPU          |

| HD6         | M4         | I/O         | CPU          |

| HD7         | L1         | 1/0         | CPU          |

| HD8         | L2         | 1/0         | CPU          |

| HD9         | L3         | 1/0         | CPU          |

| HD10        | L4         | 1/0         | CPU          |

| HD11        | L5         | 1/0         | CPU          |

| HD12        | K1         | 1/0         | CPU          |

| HD13        | K2         | 1/0         | CPU          |

| HD14        | K3         | 1/0         | CPU          |

| HD15        | K4         | 1/0         | CPU          |

| HD16        | J1         | 1/0         | CPU          |

| HD17        | J2         | 1/0         | CPU          |

| HD18        | J3         | 1/0         | CPU          |

| HD19        | J4         | 1/0         | CPU          |

| HD20        | J5         | 1/0         | CPU          |

| HD21        | H1         | 1/0         | CPU          |

| HD22        | H2         | 1/0         | CPU          |

| HD23        | H3         | 1/0         | CPU          |

| HD24        | П3<br>Н4   |             |              |

| HD25        | H5         | I/O<br>I/O  | CPU          |

| HD26        | G1         | 1/0         | CPU          |

|             |            |             |              |

| HD27        | G2         | 1/0         | CPU          |

| HD28        | G3         | 1/0         | CPU          |

| HD29        | G4         | 1/0         | CPU          |

| HD30        | F1         | 1/0         | CPU          |

| HD31        | F2         | 1/0         | CPU          |

| HD32        | F3         | 1/0         | CPU          |

| HD33        | F4         | 1/0         | CPU          |

| HD34        | F5         | 1/0         | CPU          |

| HD35        | E1         | 1/0         | CPU          |

| HD36        | E2         | 1/0         | CPU          |

| HD37        | E3         | 1/0         | CPU          |

| HD38        | E4         | 1/0         | CPU          |

| HD39        | D1         | 1/0         | CPU          |

| HD40        | D2         | 1/0         | CPU          |

| HD41        | D3         | I/O         | CPU          |

| HD42        | D4         | I/O         | CPU          |

| HD43        | C1         | I/O         | CPU          |

| Signal Name        | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|--------------------|------------|-------------|--------------|

| HD44               | C2         | I/O         | CPU          |

| HD45               | C3         | I/O         | CPU          |

| HD46               | B1         | I/O         | CPU          |

| HD47               | B2         | I/O         | CPU          |

| HD48               | A1         | I/O         | CPU          |

| HD49               | A2         | I/O         | CPU          |

| HD50               | A3         | I/O         | CPU          |

| HD51               | B3         | I/O         | CPU          |

| HD52               | A4         | I/O         | CPU          |

| HD53               | B4         | I/O         | CPU          |

| HD54               | C4         | I/O         | CPU          |

| HD55               | A5         | I/O         | CPU          |

| HD56               | B5         | I/O         | CPU          |

| HD57               | C5         | I/O         | CPU          |

| HD58               | D5         | 1/0         | CPU          |

| HD59               |            |             |              |

| HD60               | A6<br>B6   | I/O<br>I/O  | CPU          |

| HD61               | C6         |             | CPU          |

|                    |            | 1/0         |              |

| HD62               | D6         | 1/0         | CPU          |

| HD63               | E6         | I/O         | CPU          |

| HITM#              | R4         | - 1         | CPU          |

| IGERR#             | AC6        | I/O         | CPU          |

| INTR               | AF5        | 0           | CPU          |

| IO16#+PIO18        | W23        | I/O         | ISA          |

| IOCHRDY            | AB26       | I/O         | ISA          |

| IOR#+IDE1_DRD#     | AB24       | I/O         | ISA          |

| IOW#+IDE1_DWR#     | AB25       | I/O         | ISA          |

| IRDY#              | AB11       | 1/0         | PCI          |

| IRQ1+PIO10         | AF18       | I/O         | PCI          |

| IRQ3/IRQA          | AC19       | 1           | PCI          |

| IRQ4/IRQB          | AD19       | - 1         | PCI          |

| IRQ5/IRQC          | AE19       | ı           | PCI          |

| IRQ6/IRQD          | AF19       | ı           | PCI          |

| IRQ7/IRQE          | AD20       | 1           | ISA          |

| IRQ8#+PIO11        | AE20       | I/O         | ISA          |

| IRQ9/IRQF          | AF20       | I           | ISA          |

| IRQ10/IRQG         | AB22       | ī           | ISA          |

| IRQ11/IRQH         | AC21       | -           | ISA          |

| IRQ12+PIO12        | AD21       | I/O         | ISA          |

| IRQ14+PIO13        | AE21       | 1/0         | ISA          |

| IRQ15+SIN#         |            | I           | ISA          |

|                    | AF21       |             |              |

| IRQSER+SDCKE+SOUT# | AE18       | 1/0         | PCI          |

| KBDCS#+PIO24+DRD#  | J26        | 1/0         | ISA          |

| KEN#               | R2         | 0           | CPU          |

| LOCK#              | U2         | - 1         | CPU          |

| M/IO#              | Y5         | 1           | CPU          |

| M16#+PIO19         | W24        | I/O         | ISA          |

| MA0                | D12        | 0           | DRAM         |

| MA1                | A13        | 0           | DRAM         |

| MA2                | B13        | 0           | DRAM         |

| MA3                | C13        | 0           | DRAM         |

| MA4                | D13        | 0           | DRAM         |

| MA5                | A14        | 0           | DRAN         |

| MA6                | B14        | 0           | DRAM         |

| MA7                | C14        | 0           | DRAM         |

| MA8                | D14        | 0           | DRAM         |

| -                  |            |             | DRAM         |

| Signal Name | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|-------------|------------|-------------|--------------|

| MA10        | B15        | 0           | DRAM         |

| MA11        | C15        | 0           | DRAM         |

| MD0         | G22        | I/O         | DRAM         |

| MD1         | G23        | I/O         | DRAM         |

| MD2         | G24        | I/O         | DRAM         |

| MD3         | G25        | I/O         | DRAM         |

| MD4         | G26        | I/O         | DRAM         |

| MD5         | F22        | I/O         | DRAM         |

| MD6         | F23        | I/O         | DRAM         |

| MD7         | F24        | I/O         | DRAM         |

| MD8         | F25        | I/O         | DRAM         |

| MD9         | F26        | I/O         | DRAM         |

| MD10        | E23        | I/O         | DRAM         |

| MD11        | E24        | I/O         | DRAM         |

| MD12        | E25        | I/O         | DRAM         |

| MD13        | E26        | I/O         | DRAM         |

| MD14        | D24        | I/O         | DRAM         |

| MD15        | D25        | I/O         | DRAM         |

| MD16        | D26        | I/O         | DRAM         |

| MD17        | C25        | I/O         | DRAM         |

| MD18        | C26        | I/O         | DRAM         |

| MD19        | B26        | I/O         | DRAM         |

| MD20        | A26        | I/O         | DRAM         |

| MD21        | B25        | I/O         | DRAM         |

| MD22        | A25        | I/O         | DRAM         |

| MD23        | C24        | I/O         | DRAM         |

| MD24        | B24        | I/O         | DRAM         |

| MD25        | A24        | I/O         | DRAM         |

| MD26        | D23        | I/O         | DRAM         |

| MD27        | C23        | I/O         | DRAM         |

| MD28        | B23        | I/O         | DRAM         |

| MD29        | A23        | I/O         | DRAM         |

| MD30        | D22        | I/O         | DRAM         |

| MD31        | C22        | I/O         | DRAM         |

| MD32        | B22        | I/O         | DRAM         |

| MD33        | A22        | I/O         | DRAM         |

| MD34        | E21        | I/O         | DRAM         |

| MD35        | D21        | I/O         | DRAM         |

| MD36        | C21        | I/O         | DRAM         |

| MD37        | B21        | I/O         | DRAM         |

| MD38        | A21        | I/O         | DRAM         |

| MD39        | D20        | I/O         | DRAM         |

| MD40        | C20        | I/O         | DRAM         |

| MD41        | B20        | I/O         | DRAM         |

| MD42        | A20        | I/O         | DRAM         |

| MD43        | E19        | I/O         | DRAM         |

| MD44        | D19        | I/O         | DRAM         |

| MD45        | C19        | I/O         | DRAM         |

| MD46        | B19        | I/O         | DRAM         |

| MD47        | A19        | I/O         | DRAM         |

| MD48        | E18        | I/O         | DRAM         |

| MD49        | D18        | I/O         | DRAM         |

| MD50        | C18        | I/O         | DRAM         |

| MD51        | B18        | I/O         | DRAM         |

| MD52        | A18        | I/O         | DRAM         |

| MD53        | D17        | I/O         | DRAM         |

| MD54        | C17        | I/O         | DRAM         |

|             |            |             |              |

| Signal Name                      | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|----------------------------------|------------|-------------|--------------|

| MD55                             | B17        | I/O         | DRAM         |

| MD56                             | A17        | I/O         | DRAM         |

| MD57                             | E16        | I/O         | DRAM         |

| MD58                             | D16        | I/O         | DRAM         |

| MD59                             | C16        | I/O         | DRAM         |

| MD60                             | B16        | I/O         | DRAM         |

| MD61                             | A16        | I/O         | DRAM         |

| MD62                             | E15        | I/O         | DRAM         |

| MD63                             | D15        | I/O         | DRAM         |

| MRD#+IDE1_DCS3#                  | AC26       | I/O         | ISA          |

| MWR#+IDE1_DCS1#                  | AB23       | I/O         | ISA          |

| NA#                              | U4         | 0           | CPU          |

| NMI                              | AD5        | 0           | CPU          |

| OSC_14MHZ                        | E5         | ı           | CORE         |

| OSC32                            | C7         | ı           | CORE         |

| PCICLK0+PIO0                     | AB14       | I/O         | PCI          |

| PCICLKIN                         | AB6        | 1           | CORE         |

| PERR#                            | AE17       | I/O         | PCI          |

| PLOCK#                           | AE15       | I/O         | PCI          |

| PPWRL+PPWR0#+PCTLH               | AC23       | 0           | ISA          |

| PWRGD                            | H26        | 1           | ISA          |

| RAS0#+SDCS0#                     | E12        | 0           | DRAM         |

| RAS1#+SDCS1#                     | E13        | 0           | DRAM         |

| RAS2#+SDCS2#                     | B12        | 0           | DRAM         |

| RAS3#+SDCS3#+MA12                | C12        | 0           | DRAM         |

| RAS4#+SDCS4#+MA12                | E22        | 0           | DRAM         |

| RFSH#+PPWR12                     | J25        | 1/0         | ISA          |

| REQ0#                            | AF17       | ı, C        | PCI          |

| REQ1#+PIO7                       | AB18       | I/O         | PCI          |

| REQ2#+PIO8                       | AE16       | I/O         | PCI          |

| REQ3#                            | AD18       | 1           | PCI          |

| RESET#                           | AC24       | 0           | ISA          |

| ROMCS#+PIO23+<br>ROMCS#/KBDCS#   | J24        | I/O         | ISA          |

| RSTDRV+PIO15+PCTLL               | AC25       | I/O         | ISA          |

| RTCAS+IDE1_DA0                   | N24        | I/O         | ISA          |

| RTCRD#+IDE1_DA1                  | N25        | I/O         | ISA          |

| RTCWR#+IDE1_DA2                  | N26        | I/O         | ISA          |

| SA0+IDE1_DD0                     | N23        | I/O         | ISA          |

| SA1+IDE1_DD1                     | N22        | I/O         | ISA          |

| SA2+IDE1_DD2                     | P26        | I/O         | ISA          |

| SA3+IDE1_DD3                     | P25        | I/O         | ISA          |

| SA4+IDE1_DD4                     | P24        | I/O         | ISA          |

| SA5+IDE1_DD5                     | P23        | I/O         | ISA          |

| SA6+IDE1_DD6                     | R26        | I/O         | ISA          |

| SA7+IDE1_DD7                     | R25        | I/O         | ISA          |

| SA8+IDE1_DD8                     | R24        | I/O         | ISA          |

| SA9+IDE1_DD9                     | R23        | I/O         | ISA          |

| SA10+IDE1_DD10                   | R22        | I/O         | ISA          |

| SA11+IDE1_DD11                   | T26        | I/O         | ISA          |

| SA12+IDE1_DD12                   | T25        | I/O         | ISA          |

|                                  | T24        | I/O         | ISA          |

| SA13+IDE1_DD13                   |            | I/O         | ISA          |

|                                  | 123        |             |              |

| SA14+IDE1_DD14                   | T23        |             | ISA          |

| SA14+IDE1_DD14<br>SA15+IDE1_DD15 | T22        | I/O         | ISA<br>ISA   |

| SA14+IDE1_DD14                   |            |             | ISA<br>ISA   |

|                           | 1          |             |              |

|---------------------------|------------|-------------|--------------|

| Signal Name               | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

| SA19+PPWR9                | U23        | I/O         | ISA          |

| SA20+PPWR0                | V26        | I/O         | ISA          |

| SA21+PPWR1                | V25        | I/O         | ISA          |

| SA22+PPWR2                | V24        | I/O         | ISA          |

| SA23+PPWR3                | V23        | I/O         | ISA          |

| SBHE#+PIO20               | W25        | I/O         | ISA          |

| SD0+MAD0                  | AD26       | I/O         | ISA          |

| SD1+MAD1                  | AD25       | I/O         | ISA          |

| SD2+MAD2                  | AD24       | I/O         | ISA          |

| SD3+MAD3                  | AE26       | I/O         | ISA          |

| SD4+MAD4                  | AE25       | I/O         | ISA          |

| SD5+MAD5                  | AF26       | I/O         | ISA          |

| SD6+MAD6                  | AF25       | I/O         | ISA          |

| SD7+MAD7                  | AF24       | I/O         | ISA          |

| SD8+MAD8                  | AE24       | I/O         | ISA          |

| SD9+MAD9                  | AF23       | I/O         | ISA          |

| SD10+MAD10                | AE23       | 0           | ISA          |

| SD11+MAD11                | AD23       | I/O         | ISA          |

| SD12+MAD12                | AF22       | I/O         | ISA          |

| SD13+MAD13                | AE22       | I/O         | ISA          |

| SD14+MAD14                | AD22       | I/O         | ISA          |

| SD15+MAD15                | AC22       | I/O         | ISA          |

| SDCAS#                    | A8         | 0           | DRAM         |

| SDRAS#                    | D7         | 0           | DRAM         |

| SEL#/ATB#+SDCKE+<br>PIO14 | AC20       | I/O         | ISA          |

| SERR#                     | AD17       | I/O         | PCI          |

| SMI#                      | AE5        | 0           | CPU          |

| SMIACT#                   | U1         | ı           | CPU          |

| SMRD#+PIO21               | W26        | I/O         | ISA          |

| SMWR#+PIO22               | V22        | I/O         | ISA          |

| SPKOUT                    | H23        | I/O         | ISA          |

| STOP#                     | AC16       | I/O         | PCI          |

| STPCLK#                   | AE6        | 0           | CPU          |

| TAG0                      | E9         | I/O         | DRAM         |

| TAG1                      | D9         | I/O         | DRAM         |

| TAG2                      | C9         | I/O         | DRAM         |

| TAG3                      | B9         | I/O         | DRAM         |

| TAG4                      | A9         | I/O         | DRAM         |

| TAG5                      | D8         | I/O         | DRAM         |

| TAG6                      | C8         | I/O         | DRAM         |

| TAG7                      | B8         | I/O         | DRAM         |

| TAGWE#                    | A10        | 0           | DRAM         |

| TC+PPWR10+IDEDIR          | M23        | I/O         | ISA          |

| MA13+DCC                  | В7         | I/O         | DRAM         |

| SDCKE                     | A7         | I/O         | DRAM         |

| TMS                       | AB5        | I/O         | CPU          |

| TRDY#                     | AB12       | I/O         | PCI          |

| VCC_CORE                  | H22        | Р           |              |

| VCC_CORE                  | K5         | Р           |              |

| VCC CORE                  | AB19       | P           |              |

| VCC_CPU                   | E8         | P           |              |

| VCC_CPU                   | G5         | P           |              |

| VCC CPU                   | T5         | P           |              |

| VCC_CPU                   | W5         | P           |              |

| VCC_DRAM                  | E11        | P           |              |

| VCC_DRAM                  | E17        | P           |              |

| VOO_DITAIVI               | L17        | r           |              |

| Signal Name    | Pin<br>No. | Pin<br>Type | Pwr<br>Plane |

|----------------|------------|-------------|--------------|

| VCC_DRAM       | E20        | Р           |              |

| VCC_ISA        | L22        | Р           |              |

| VCC_ISA        | U22        | Р           |              |

| VCC_ISA        | Y22        | Р           |              |

| VCC_PCI        | AB7        | Р           |              |

| VCC_PCI        | AB10       | Р           |              |

| VCC_PCI        | AB16       | Р           |              |

| W/R#+INV       | AA5        | I/O         | CPU          |

| XD0+IDE_DWR#   | Y26        | I/O         | ISA          |

| XD1+IDE_DRD#   | Y25        | I/O         | ISA          |

| XD2+IDE_DA0    | Y24        | 1/0         | ISA          |

| XD3+IDE_DA1    | Y23        | I/O         | ISA          |

| XD4+IDE_DA2    | AA26       | I/O         | ISA          |

| XD5+IDE_DDACK# | AA25       | I/O         | ISA          |

| XD6+IDE_DCS1#  | AA24       | I/O         | ISA          |

| XD7+IDE_DCS3#  | AA23       | I/O         | ISA          |

| 5VREF          | AB21       | Р           |              |

| 5VREF          | E7         | Р           |              |

#### Power Plane Key:

CORE = 3.3V Only CPU = 3.3V/2.5V DRAM = 3.3V or 5.0V ISA = 3.3V or 5.0V PCI = 3.3V or 5.0V

Note: The pins listed below are 5.0V tolerant inputs, even when their power plane is connected to 3.3V as long as the 5VREF pins of FireStar are connected to +5.0V:

OSC32 OSC\_14MHZ PCICLK IRQA IRQB IRQC IRQD IRQ1

912-4000-013 Revision: 1.0

#### **Clock Signal Specifications** 3.0

#### 3.1 **CPU Input Clock Recommendations**

Ideal FireStar input clock skew, relative to CPU clock: early by 3.5ns ± 0.5ns

The complete CPU clock specification is provided below. Note that timings for 2.5V CPUs are not yet available, but will be provided in the next FireStar bulletin.

| CPU Clock Recommendations (66MHz, 3.3V)  | Min   | Max   |

|------------------------------------------|-------|-------|

| Clock Period                             | 15ns  |       |

| Duty Cycle                               | 60/40 | 40/60 |

| Clock High Time <sup>a</sup>             | 6ns   | 9ns   |

| Clock Low Time <sup>b</sup>              | 6ns   | 9ns   |

| Clock Rise Time, 0.0V to 2.0V            | 1ns   | 2ns   |

| Clock Fall Time, 2.0V to 0.0V            | 1ns   | 2ns   |

| Clock Jitter                             | 0ns   | 0.5ns |

| Clock Skew, FireStar to CPU <sup>c</sup> | 3.0ns | 4.0ns |

- a. 2V and above.

- b. 0.8V and below.

- c. Measured at 1.5V on rising edge of both clocks.